## Dual 12-/10-Bit 500 MSPS Digital-to-Analog Converters

Check for Samples: DAC3154, DAC3164

### **FEATURES**

- Dual Channel

- Resolution

DAC3154: 10-BitDAC3164: 12-Bit

- Maximum Sample Rate: 500 MSPS

- Pin Compatible Family with DAC3174 and DAC3151/DAC3161/DAC3171

- Input Interface:

- 12-/10-Bit Wide LVDS Inputs

- Internal FIFO

- Chip to Chip Synchronization

- Power Dissipation: 460mW

- Spectral Performance at 20 MHz IF

- SNR: 62 dBFS for DAC3154, 72 dBFS for DAC3164

- SFDR: 76 dBc for DAC3154, 77 dBc for DAC3164

- Current Sourcing DACs

- Compliance Range: -0.5V to 1V

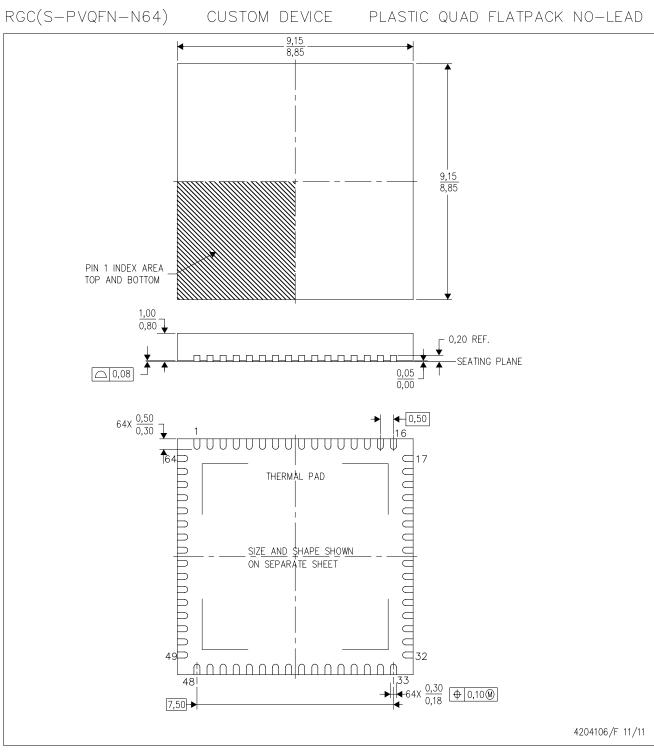

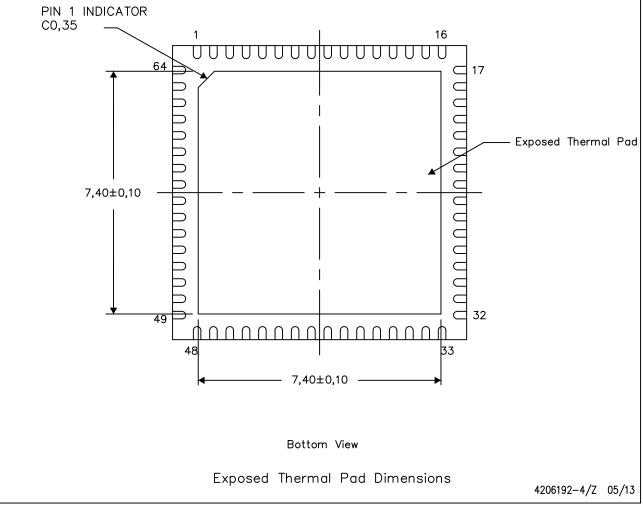

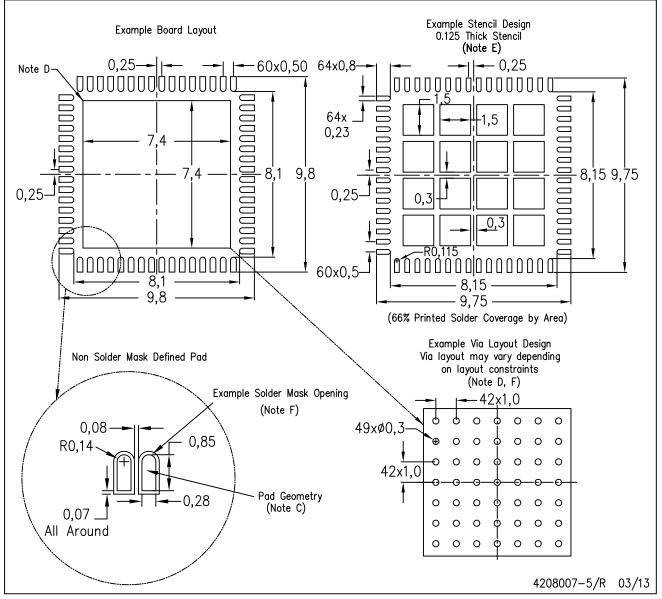

Package: 64 Pin QFN (9x9mm)

### **APPLICATIONS**

- Multi-Carrier, Multi-Mode Cellular Infrastructure Base Stations

- Radar

- Signal Intelligence

- Software-Defined Radio

- Test and Measurement Instrumentation

#### DESCRIPTION

The DAC3154/DAC3164 are dual channel 10-/12-bit, pin-compatible family of 500 MSPS digital-to-analog converters (DAC). The DAC3154/DAC3164 use a 10-/12-bit wide LVDS digital bus with an input FIFO. FIFO input and output pointers can be synchronized multiple devices across for precise synchronization. The DAC outputs are current sourcing and terminate to GND with a compliance range of -0.5 to 1V. DAC3154/ DAC3164 are pin compatible with the dual-channel, 14-bit, 500 MSPS digital-to-analog converters DAC3174, and the singlechannel, 14-/12-10-bit, digital-to-analog converters DAC3171/DAC3161/DAC3151.

The devices are available in a QFN-64 PowerPAD™ package is specified over the full industrial temperature range (-40°C to 85°C).

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

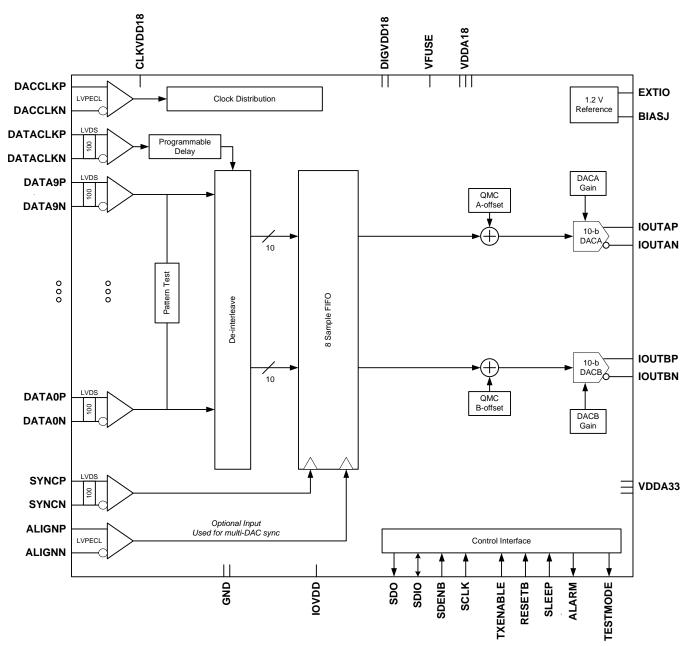

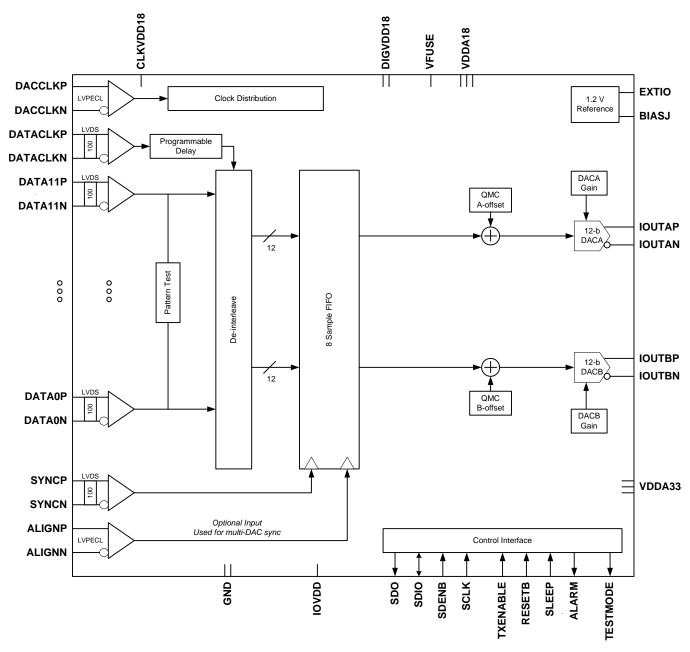

## **BLOCK DIAGRAMS**

Figure 1. DAC3154

Figure 2. DAC3164

## TEXAS INSTRUMENTS

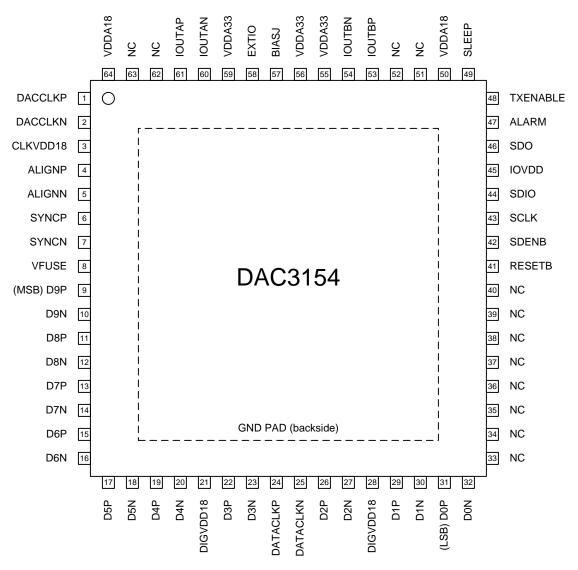

#### PINOUT - DAC3154

### PIN ASSIGNMENT TABLE - DAC3154

|            |      | 1   | THE ACCIONMENT TABLE DAGGET                                                                                                                                                                                            |

|------------|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN        |      | 1/0 | DESCRIPTION                                                                                                                                                                                                            |

| NAME       | NO.  |     | DESCRIPTION                                                                                                                                                                                                            |

| CONTROL/SE | RIAL | •   |                                                                                                                                                                                                                        |

| SCLK       | 43   | - 1 | Serial interface clock. Internal pull-down.                                                                                                                                                                            |

| SDENB      | 42   | - 1 | Serial interface clock. Internal pull-up.                                                                                                                                                                              |

| SDIO       | 44   | I/O | Bi-directional serial data in 3 pin mode (default). In 4-pin interface mode (register XYZ), the SDIO pin in an input only. Internal Pull-down.                                                                         |

| SDO        | 46   | 0   | Uni-directional serial interface data in 4 pin mode (register XYZ). The SDO pin is tri-stated in 3-pin interface mode (default). Internal Pulldown.                                                                    |

| RESETB     | 41   | I   | Serial interface reset input. Active low. Initialized internal registers during high to low transition. Assynchronous. Internal pull-up.                                                                               |

| ALARM      | 47   | 0   | CMOS output for ALARM condition.                                                                                                                                                                                       |

| TXENABLE   | 48   | I   | Transmit enable active high input. TXENABLE must be high for the DATA to the DAC to be enabled. When TXENABLE is low, the digital logic section is forced to all 0, and any input data is ignored. Internal pull-down. |

| SLEEP      | 49   | I   | Puts device in sleep, active high. Internal pull-down.                                                                                                                                                                 |

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

www.ti.com

## PIN ASSIGNMENT TABLE - DAC3154 (continued)

| PIN          |                             |     | DECODINE                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|--------------|-----------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| NAME         | NO.                         | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| DATA INTERFA | ACE                         | •   |                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

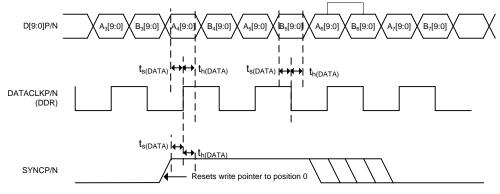

| DATA[9:0]P/N | 9/10-<br>19/20<br>22/23     | I   | LVDS input data bits for both channels. Each positive/negative LVDS pair has an internal 100 $\Omega$ termination resistor. Data format relative to DATACLKP/N clock is Double Data Rate (DDR) with two data transfers per DATACKP/N clock cycle.                                                |  |  |  |  |  |

|              | 26/27-                      |     | The data format is interleaved with channel A (rising edge) and channel B falling edge.                                                                                                                                                                                                          |  |  |  |  |  |

|              | 31/32                       |     | In the default mode (reverse bus not enabled):                                                                                                                                                                                                                                                   |  |  |  |  |  |

|              |                             |     | DATA9P/N is most significant data bit (MSB)                                                                                                                                                                                                                                                      |  |  |  |  |  |

|              |                             |     | DATA0P/N is most significant data bit (LSB)                                                                                                                                                                                                                                                      |  |  |  |  |  |

| DATACLKP/N   | 24/25                       | I   | DDR differential input data clock. Edge to center nominal timing. Ch A rising edge, Ch B falling edge in multiplexed output mode.                                                                                                                                                                |  |  |  |  |  |

| SYNCP/N      | 6/7                         | I   | Reset the FIFO or to be used as a syncing source. These two functions are captured with the rising edge of DATACLKP/N. The signal captured by the falling edge of DATACLKP/N.                                                                                                                    |  |  |  |  |  |

| ALIGNP/N     | 4/5                         | I   | LVPECL FIFO output syncrhonization. This positive/negative pair is captured with the rising edge of DACCLKP/N. It is used to reset the clock dividers and for multiple DAC synchronization. If unused it can be left unconnected.                                                                |  |  |  |  |  |

| OUTPUT/CLOC  | K                           |     |                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| DACCLKP/N    | 1/2                         | I   | LVPECL clock input for DAC core with a self-bias of approximately CLKVDD18/2.                                                                                                                                                                                                                    |  |  |  |  |  |

| IOUTAP/N     | 61/60                       | 0   | A-Channel DAC current output. An offset binary data pattern of 0x0000 at the DAC input results in a full scale current source and the most positive voltage on the IOUTAP pin. Similarly, a 0xFFFF data input results in a 0 mA current source and the least positive voltage on the IOUTAP pin. |  |  |  |  |  |

| IOUTBP/N     | 53/54                       | 0   | B-Channel DAC current output. An offset binary data pattern of 0x0000 at the DAC input results in a full scale current source and the most positive voltage on the IOUTBP pin. Similarly, a 0xFFFF data input results in a 0 mA current source and the least positive voltage on the IOUTBP pin. |  |  |  |  |  |

| REFERENCE    |                             | -   |                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| EXTIO        | 58                          | I/O | Used as external reference input when internal reference is disabled. Requires a 0.1 µF decoupling capacitor to GND when used as reference output.                                                                                                                                               |  |  |  |  |  |

| BIASJ        | 57                          | 0   | Full-scale output current bias. For 20 mA full-scale output current, connect a 960 $\Omega$ resistor to GND.                                                                                                                                                                                     |  |  |  |  |  |

| POWER SUPPI  | _Y                          |     |                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| IOVDD        | 45                          | I   | Supply voltage for CMOS IO's. 1.8V – 3.3V.                                                                                                                                                                                                                                                       |  |  |  |  |  |

| CLKVDD18     | 3                           | I   | 1.8V clock supply                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| DIGVDD18     | 21, 28                      | I   | 1.8V digital supply. Also supplies LVDS receivers.                                                                                                                                                                                                                                               |  |  |  |  |  |

| VDDA18       | 50, 64                      | I   | Analog 1.8V supply                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| VDDA33       | 55, 56,<br>59               | I   | Analog 3.3V supply                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| VFUSE        | 8                           | I   | Digital supply voltage. (1.8V) This supply pin is also used for factory fuse programming. Connect to DVDD pins for normal operation.                                                                                                                                                             |  |  |  |  |  |

| NC           | 33-40,<br>51, 52,<br>62, 63 |     | Not used. These pins can be left open or tied to GROUND in actual application use.                                                                                                                                                                                                               |  |  |  |  |  |

## TEXAS INSTRUMENTS

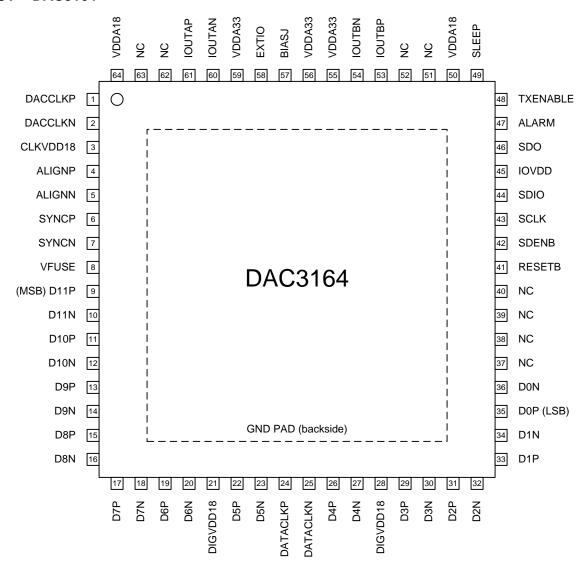

## PINOUT - DAC3164

### PIN ASSIGNMENT TABLE - DAC3164

|             |     |     | THE ACCIONMENT TABLE DAGGIOT                                                                                                                                                                                           |

|-------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN         | 1   | 1/0 | DESCRIPTION                                                                                                                                                                                                            |

| NAME        | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                            |

| CONTROL/SER | IAL |     |                                                                                                                                                                                                                        |

| SCLK        | 43  | I   | Serial interface clock. Internal pull-down.                                                                                                                                                                            |

| SDENB       | 42  | I   | Serial interface clock. Internal pull-up.                                                                                                                                                                              |

| SDIO        | 44  | I/O | Bi-directional serial data in 3 pin mode (default). In 4-pin interface mode (register XYZ), the SDIO pin in an input only. Internal Pull-down.                                                                         |

| SDO         | 46  | 0   | Uni-directional serial interface data in 4 pin mode (register XYZ). The SDO pin is tri-stated in 3-pin interface mode (default). Internal Pulldown.                                                                    |

| RESETB      | 41  | I   | Serial interface reset input. Active low. Initialized internal registers during high to low transition. Assynchronous. Internal pull-up.                                                                               |

| ALARM       | 47  | 0   | CMOS output for ALARM condition.                                                                                                                                                                                       |

| TXENABLE    | 48  | I   | Transmit enable active high input. TXENABLE must be high for the DATA to the DAC to be enabled. When TXENABLE is low, the digital logic section is forced to all 0, and any input data is ignored. Internal pull-down. |

| SLEEP       | 49  | I   | Puts device in sleep, active high. Internal pull-down.                                                                                                                                                                 |

## PIN ASSIGNMENT TABLE - DAC3164 (continued)

| PIN            |                                        |     |                                                                                                                                                                                                                                                                                                                                              |

|----------------|----------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME           | NO.                                    | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                  |

| DATA INTERFACE |                                        |     |                                                                                                                                                                                                                                                                                                                                              |

| DATA[11:0]P/N  | 9/10-<br>19/20<br>22/23,               | I   | LVDS input data bits for both channels. Each positive/negative LVDS pair has an internal 100 $\Omega$ termination resistor. Data format relative to DATACLKP/N clock is Double Data Rate (DDR) with two data transfers per DATACKP/N clock cycle.                                                                                            |

|                | 26-27-<br>35/36                        |     | The data format is interleaved with channel A (rising edge) and channel B falling edge.                                                                                                                                                                                                                                                      |

|                | 33/30                                  |     | In the default mode (reverse bus not enabled):                                                                                                                                                                                                                                                                                               |

|                |                                        |     | DATA11P/N is most significant data bit (MSB)                                                                                                                                                                                                                                                                                                 |

|                |                                        |     | DATA0P/N is most significant data bit (LSB)                                                                                                                                                                                                                                                                                                  |

| DATACLK[:0]P/N | 24/25                                  | I   | DDR differential input data clock. Edge to center nominal timing. Ch A rising edge, Ch B falling edge in multiplexed output mode.                                                                                                                                                                                                            |

| SYNCP/N        | 6/7                                    | I   | Reset the FIFO or to be used as a syncing source. These two functions are captured with the rising edge of DATACLKP/N. The signal captured by the falling edge of DATACLKP/N.                                                                                                                                                                |

| ALIGNP/N       | 24/25                                  | I   | LVPECL FIFO output syncrhonization. This positive/negative pair is captured with the rising edge of DACCLKP/N. It is used to reset the clock dividers and for multiple DAC synchronization. If unused it can be left unconnected.                                                                                                            |

| OUTPUT/CLOCK   |                                        | •   |                                                                                                                                                                                                                                                                                                                                              |

| DACCLKP/N      | 1/2                                    | I   | LVPECL clock input for DAC core with a self-bias of approximately CLKVDD18/2.                                                                                                                                                                                                                                                                |

| IOUTAP/N 61/60 |                                        |     | A-Channel DAC current output. An offset binary data pattern of 0x0000 at the DAC input results in a full scale current source and the most positive voltage on the IOUTA1 pin. Similarly, a 0xFFFF data input results in a 0 mA current source and the least positive voltage on the IOUTA1 pin. The IOUTA2 pin is the complement of IOUTA1. |

| IOUTBP/N       | 53/54                                  | 0   | B-Channel DAC current output. An offset binary data pattern of 0x0000 at the DAC input results in a full scale current source and the most positive voltage on the IOUTB1 pin. Similarly, a 0xFFFF data input results in a 0 mA current source and the least positive voltage on the IOUTB1 pin. The IOUTB2 pin is the complement of IOUTB1. |

| REFERENCE      | !                                      | •   |                                                                                                                                                                                                                                                                                                                                              |

| EXTIO          | 58                                     | I/O | Used as external reference input when internal reference is disabled. Requires a 0.1 µF decoupling capacitor to GND when used as reference output.                                                                                                                                                                                           |

| BIASJ          | 57                                     | 0   | Full-scale output current bias. For 20 mA full-scale output current, connect a 960 $\Omega$ resistor to GND.                                                                                                                                                                                                                                 |

| POWER SUPPLY   |                                        |     |                                                                                                                                                                                                                                                                                                                                              |

| IOVDD          | 45                                     | ı   | Supply voltage for CMOS IO's. 1.8V – 3.3V.                                                                                                                                                                                                                                                                                                   |

| CLKVDD18       | 3                                      | ı   | 1.8V clock supply                                                                                                                                                                                                                                                                                                                            |

| DIGVDD18       | 21, 28                                 | ı   | 1.8V digital supply. Also supplies LVDS receivers.                                                                                                                                                                                                                                                                                           |

| VDDA18         | 50, 64                                 | ı   | Analog 1.8V supply                                                                                                                                                                                                                                                                                                                           |

| VDDA33         | 55, 56,<br>59                          | I   | Analog 3.3V supply                                                                                                                                                                                                                                                                                                                           |

| VFUSE          | 8                                      | I   | Digital supply voltage. (1.8V) This supply pin is also used for factory fuse programming. Connect to DVDD pins for normal operation.                                                                                                                                                                                                         |

| NC             | 37, 38,<br>39, 40,<br>51, 52<br>62, 63 |     | Not used. These pins can be left open or tied to GROUND in actual application use.                                                                                                                                                                                                                                                           |

## PACKAGE/ORDERING INFORMATION(1)

| PRODUCT | PACKAGE-<br>LEAD | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | ECO PLAN                  | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA | QUANTITY |

|---------|------------------|-----------------------|-----------------------------------|---------------------------|--------------------|--------------------|----------|

| DAC3154 |                  |                       |                                   |                           | DAC3154IRGCT       |                    | 250      |

| DAC3154 |                  |                       |                                   |                           | DAC3154IRGCR       |                    | 2000     |

|         | QFN-64           | RGC                   | -40°C to 85°C                     | GREEN (RoHS and no Sb/Br) | DAC3164IRGC25      | Tape and Reel      | 25       |

| DAC3164 |                  |                       |                                   | a.i.a iio 02/2:/          | DAC3164IRGCT       |                    | 250      |

|         |                  |                       |                                   |                           | DAC3164IRGCR       |                    | 2000     |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

Product Folder Links: DAC3154 DAC3164

## **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

|                        |                                                           | VALUE                  | UNIT |

|------------------------|-----------------------------------------------------------|------------------------|------|

|                        | VDDA33 to GND                                             | -0.5 to 4              |      |

|                        | VDDA18 to GND                                             | -0.5 to 2.3            |      |

| Supply voltage         | CLKVDD18 to GND                                           | -0.5 to 2.3            | V    |

|                        | IOVDD to GND                                              | -0.5 to 4              |      |

|                        | DIGVDD18 to GND                                           | -0.5 to 2.3            |      |

|                        | CLKVDD18 to DIGVDD18                                      | -0.5 to 0.5            |      |

|                        | VDDA18 to DIGVDD18                                        | -0.5 to 0.5            |      |

|                        | D[110]P, D[110]N, DATACLKP, DATACLKN, SYNCP, SYNCN to GND | -0.5 to DIGVDD18 + 0.5 |      |

| Terminal voltage range | DACCLKP, DACCLKN, ALIGNP, ALIGNN                          | -0.5 to CLKVDD18 + 0.5 | V    |

| range                  | TXENABLE, ALARM, SDO, SDIO, SCLK, SDENB, RESETB to GND    | -0.5 to IOVDD + 0.5    |      |

|                        | IOUTAP, IOUTAN, IOUTBP, IOUTBN to GND                     | -0.7 to 1.4            |      |

|                        | VDDA33 to GND                                             |                        |      |

| Storage temperature    | e range                                                   | -65 to 150             | °C   |

| ESD, Human Body I      | Model                                                     | 2                      | kV   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### THERMAL INFORMATION

|                  | Junction-to-case (top) thermal resistance  Junction-to-board thermal resistance  Junction-to-top characterization parameter  Junction-to-board characterization parameter | DAC3174      |        |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------|

|                  |                                                                                                                                                                           | QFN (64 PIN) | UNITS  |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance                                                                                                                                    | 23.0         |        |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance                                                                                                                                 | 7.6          |        |

| $\theta_{JB}$    | Junction-to-board thermal resistance                                                                                                                                      | 2.8          | °C/W   |

| ΨЈТ              | Junction-to-top characterization parameter                                                                                                                                | 0.1          | - C/VV |

| ΨЈВ              | Junction-to-board characterization parameter                                                                                                                              | 2.8          |        |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance                                                                                                                              | 0.2          |        |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

Submit Documentation Feedback

Copyright © 2013, Texas Instruments Incorporated

STRUMENTS

www.ti.com SLAS960 -MAY 2013

## **ELECTRICAL CHARACTERISTICS – DC SPECIFICATIONS**

Typical values at  $T_A$  = 25°C, full temperature range is  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 85°C, DAC sample rate = 500MSPS, 50% clock duty cycle, VDDA33/IOVDD = 3.3V, VDDA18/CLKVDD18/DIGVDD18 = 1.8V, IOUT<sub>FS</sub> = 20mA (unless otherwise noted).

|           | DADAMETER                            | TEST CONDITIONS                                            | 1    | DAC3154 | 4    | [    | DAC3164 | 4    | TUALL         |

|-----------|--------------------------------------|------------------------------------------------------------|------|---------|------|------|---------|------|---------------|

|           | PARAMETER                            | TEST CONDITIONS                                            | MIN  | TYP     | MAX  | MIN  | TYP     | MAX  | UNIT          |

| Resolutio | n                                    |                                                            | 10   |         |      | 12   |         |      | Bits          |

| DC ACCU   | IRACY                                |                                                            |      |         |      |      |         |      |               |

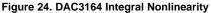

|           | DNL Differential nonlinearity        | 1 LSB = $IOUT_{FS}/2^{10}$ for                             |      | ±0.04   |      |      | ±0.2    |      |               |

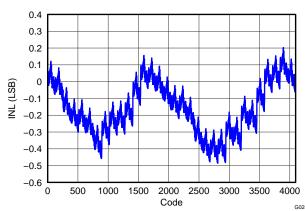

|           | INL Integral nonlinearity            | DAC3154; 1 LSB = $IOUT_{FS}/2^{12}$ for DAC3164            |      | ±0.15   |      |      | ±0.5    |      | LSB           |

| ANALOG    | OUTPUTS                              |                                                            |      |         |      |      |         |      |               |

|           | Coarse gain linearity                |                                                            |      | ±0.4    |      |      | ±0.4    |      | LSB           |

|           | Offset error                         | Mid code offset                                            |      | 0.01    |      |      | 0.01    |      | %FSR          |

|           | Cain arrar                           | With external reference                                    |      | ±2      |      |      | ±2      |      | %FSR          |

|           | Gain error                           | With internal reference                                    |      | ±2      |      |      | ±2      |      | %FSR          |

|           | Gain mismatch                        | With internal reference                                    | -2   |         | 2    | -2   |         | 2    | %FSR          |

|           | Minimum full scale output current    | Nominal full-scale current,                                |      | 2       |      |      | 2       |      | A             |

|           | Maximum full scale output current    | IOUT <sub>FS</sub> = 16xIBAIS current                      |      | 20      |      |      | 20      |      | mA            |

|           | Output compliance range              | IOUTFS = 20 mA                                             | -0.5 |         |      | -0.5 |         | 1    | V             |

|           | Output resistance                    |                                                            |      | 300     |      |      | 300     |      | kΩ            |

|           | Output capacitance                   |                                                            |      | 5       |      |      | 5       |      | pF            |

| REFEREN   | ICE OUTPUT                           |                                                            |      |         |      |      |         |      | !             |

| $V_{REF}$ | Reference output voltage             |                                                            | 1.14 | 1.2     | 1.26 | 1.14 | 1.2     | 1.26 | V             |

|           | Reference output current             |                                                            |      | 100     |      |      | 100     |      | nA            |

| REFEREN   | ICE INPUT                            |                                                            | ,    |         |      |      |         |      |               |

|           | VEXTIO Input voltage range           | External reference mode                                    | 0.1  | 1.2     | 1.25 | 0.1  | 1.2     | 1.25 | V             |

|           | Input resistance                     |                                                            |      | 1       |      |      | 1       |      | ΜΩ            |

|           | Small signal bandwidth               |                                                            |      | 500     |      |      | 500     |      | kHz           |

|           | Input capacitance                    |                                                            |      | 100     |      |      | 100     |      | pF            |

| TEMPERA   | ATURE COEFFICIENTS                   |                                                            | "    |         |      |      |         |      | li            |

|           | Offset drift                         |                                                            |      | ±1      |      |      | ±1      |      | ppm of FSR/°C |

|           |                                      | With external reference                                    |      | ±15     |      |      | ±15     |      |               |

|           | Gain drift                           | With internal reference                                    |      | ±30     |      |      | ±30     |      |               |

|           | Reference voltage drift              |                                                            |      | ±8      |      |      | ±8      |      | ppm /°C       |

| POWER S   | SUPPLY                               |                                                            |      |         |      |      |         |      |               |

|           | DIGVDD18, VFUSE, VDDA18,<br>CLKVDD18 |                                                            | 1.71 | 1.8     |      | 1.71 | 1.8     | 1.89 | V             |

|           | VDDA33                               |                                                            | 3.15 | 3.3     |      | 3.15 | 3.3     | 3.45 | V             |

|           | IOVDD                                | Sets CMOS IO voltage levels.<br>Nominal 1.8V, 2.5V or 3.3V | 1.71 |         |      | 1.71 |         | 3.45 | V             |

## **ELECTRICAL CHARACTERISTICS – DC SPECIFICATIONS (continued)**

Typical values at  $T_A$  = 25°C, full temperature range is  $T_{MIN}$  = -40°C to  $T_{MAX}$  = 85°C, DAC sample rate = 500MSPS, 50% clock duty cycle, VDDA33/IOVDD = 3.3V, VDDA18/CLKVDD18/DIGVDD18 = 1.8V, IOUT<sub>FS</sub> = 20mA (unless otherwise noted).

|                       | DADAMETED                                        | TEST CONDITIONS                                | D    | AC315 | 4     | D    | AC3164 | 4     | UNIT    |

|-----------------------|--------------------------------------------------|------------------------------------------------|------|-------|-------|------|--------|-------|---------|

|                       | PARAMETER                                        | TEST CONDITIONS                                | MIN  | TYP   | MAX   | MIN  | TYP    | MAX   | UNII    |

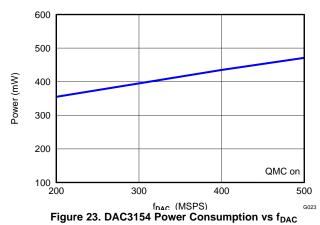

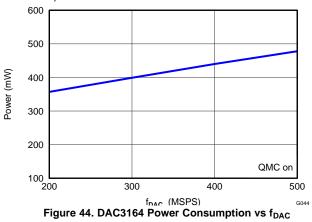

| POWER C               | CONSUMPTION                                      |                                                |      |       |       |      |        |       |         |

| I <sub>VDDA33</sub>   | 3.3V Analog supply current                       |                                                |      | 52    | 59    |      | 52     | 59    | mA      |

| I <sub>CLKVDD18</sub> | 1.8V Clock supply current                        | MODE 1                                         |      | 49    | 67    |      | 49     | 57    | mA      |

| I <sub>DIGVDD18</sub> | 1.8V Digital supply current (DIGVDD18 and VFUSE) | f <sub>DAC</sub> = 491.52 MSPS,<br>QMC on,     |      | 115   | 130   |      | 115    | 130   | mA      |

| I <sub>IOVDD</sub>    | 1.8V IO Supply current                           | IF = 20 MHz                                    |      | 0.002 | 0.015 |      | 0.002  | 0.015 | mA      |

| P <sub>dis</sub>      | Total power dissipation                          |                                                |      | 464   | 530   |      | 464    | 530   | mW      |

| I <sub>VDDA33</sub>   | 3.3V Analog supply current                       |                                                |      | 51    |       |      | 51     |       | mA      |

| I <sub>CLKVDD18</sub> | 1.8V Clock supply current                        | MODE 2                                         |      | 38    |       |      | 38     |       | mA      |

| I <sub>DIGVDD18</sub> | 1.8V Digital supply current (DIGVDD18 and VFUSE) | f <sub>DAC</sub> = 320 MSPS,<br>QMC on,        |      | 87    |       |      | 87     |       | mA      |

| I <sub>IOVDD</sub>    | 1.8V IO Supply current                           | IF = 20 MHz                                    |      | 0.002 |       |      | 0.002  |       | mA      |

| P <sub>dis</sub>      | Total power dissipation                          |                                                |      | 396   |       |      | 396    |       | mW      |

| I <sub>VDDA33</sub>   | 3.3V Analog supply current                       |                                                |      | 2.6   |       |      | 2.6    |       | mA      |

| I <sub>CLKVDD18</sub> | 1.8V Clock supply current                        | MODE 3                                         |      | 43    |       |      | 43     |       | mA      |

| I <sub>DIGVDD18</sub> | 1.8V Digital supply current (DIGVDD18 and VFUSE) | Sleep mode,<br>f <sub>DAC</sub> = 491.52 MSPS, |      | 110   |       |      | 110    |       | mA      |

| I <sub>IOVDD</sub>    | 1.8V IO Supply current                           | DAC in sleep mode                              |      | 0.003 |       |      | 0.003  |       | mA      |

| P <sub>dis</sub>      | Total power dissipation                          |                                                |      | 284   |       |      | 284    |       | mW      |

| I <sub>VDDA33</sub>   | 3.3V Analog supply current                       |                                                |      | 1.6   | 4     |      | 1.6    | 4     | mA      |

| I <sub>CLKVDD18</sub> | 1.8V Clock supply current                        | MODE 4                                         |      | 1.8   | 4     |      | 1.8    | 4     | mA      |

| I <sub>DIGVDD18</sub> | 1.8V Digital supply current (DIGVDD18 and VFUSE) | Power-down mode, no clock,                     |      |       | 1.7   |      |        | 3     | mA      |

| I <sub>IOVDD</sub>    | 1.8V IO Supply current                           | DAC in sleep mode                              |      | 0.003 | 0.015 |      | 0.003  | 0.015 | mA      |

| P <sub>dis</sub>      | Total power dissipation                          |                                                |      | 10    | 26    |      | 10     | 26    | mW      |

| PSRR                  | Power supply rejection ratio                     | DC tested                                      | -0.4 |       | 0.4   | -0.4 |        | 0.4   | %/FSR/V |

| Т                     | Operating temperature                            |                                                | -40  |       | 85    | -40  |        | 85    | °C      |

Submit Documentation Feedback

STRUMENTS

## ELECTRICAL CHARACTERISTICS – AC SPECIFICATIONS

Typical values at T  $_{\rm A}$  = 25°C, full temperature range is T  $_{\rm MIN}$  = -40°C to T  $_{\rm MAX}$  = 85°C, DAC sample rate = 500MSPS, 50% clock duty cycle, VDDA33/IOVDD = 3.3V, VDDA18/CLKVDD18/DIGVDD18 = 1.8V, IOUT  $_{\rm FS}$  = 20mA (unless otherwise noted).

|                     | DADAMETED                    | TEST COMPITIONS                                                                                                     | DAC3154 |      |     | DAC3164 |     |     | LINUT  |  |

|---------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------|---------|------|-----|---------|-----|-----|--------|--|

|                     | PARAMETER                    | TEST CONDITIONS                                                                                                     | MIN     | TYP  | MAX | MIN     | TYP | MAX | UNIT   |  |

| ANALO               | OG OUTPUT                    |                                                                                                                     |         |      |     |         |     |     |        |  |

| $f_{DAC}$           | Maximum sample rate          |                                                                                                                     | 500     |      |     | 500     |     |     | MSPS   |  |

| $t_{\text{s(DAC)}}$ | Output settling time to 0.1% | Transition: Code 0x0000 to 0x3FFF                                                                                   |         | 11   |     |         | 11  |     | ns     |  |

| $t_{PD}$            | Output propagation delay     | Does not include digital latency                                                                                    |         | 2    |     |         | 2   |     | ns     |  |

| $t_{r(IOUT)}$       | Output rise time 10% to 90%  |                                                                                                                     |         | 200  |     |         | 200 |     | ps     |  |

|                     | Output fall time 90% to 10%  |                                                                                                                     |         | 200  |     |         | 200 |     | ps     |  |

|                     | Digital Latency              | Length of delay from DAC input pins to DATA at output pins. In normal operation mode including the latency of FIFO. |         | 26   |     |         | 26  |     | μs     |  |

| AC PE               | RFORMANCE                    |                                                                                                                     |         |      |     |         |     |     |        |  |

|                     |                              | f <sub>DAC</sub> = 500 MSPS, f <sub>out</sub> = 10.1 MHz                                                            |         | 81   |     |         | 82  |     |        |  |

| SFDR                | Spurious free dynamic range  | $f_{DAC}$ = 500 MSPS, $f_{out}$ = 20.1 MHz                                                                          |         | 76   |     |         | 77  |     | dBc    |  |

|                     | 90                           | f <sub>DAC</sub> = 500 MSPS, f <sub>out</sub> = 70.1 MHz                                                            |         | 69   |     |         | 70  |     |        |  |

|                     |                              | $f_{DAC} = 500 \text{ MSPS}, f_{out} = 10.1 \pm 0.5 \text{ MHz}$                                                    |         | 82   |     |         | 83  |     |        |  |

| IMD3                | Intermodulation distortion   | $f_{DAC} = 500 \text{ MSPS}, f_{out} = 20.1 \pm 0.5 \text{ MHz}$                                                    |         | 81   |     |         | 82  |     | dBc    |  |

| נטואוו              | intermodulation distortion   | $f_{DAC} = 500 \text{ MSPS}, f_{out} = 70.1 \pm 0.5 \text{ MHz}$                                                    |         | 73.5 |     |         | 74  |     | ubc    |  |

|                     |                              | $f_{DAC} = 500 \text{ MSPS}, f_{out} = 150.1 \pm 0.5 \text{ MHz}$                                                   |         | 61   |     |         | 61  |     |        |  |

|                     |                              | $f_{DAC} = 500 \text{ MSPS}, f_{out} = 10.1 \text{ MHz}$                                                            |         | 147  |     |         | 158 |     |        |  |

| NSD                 | Noise spectral density       | $f_{DAC}$ = 500 MSPS, $f_{out}$ = 20.1 MHz                                                                          |         | 146  |     |         | 156 |     | dBc/Hz |  |

|                     |                              | $f_{DAC} = 500 \text{ MSPS}, f_{out} = 70.1 \text{ MHz}$                                                            |         | 146  |     |         | 153 |     |        |  |

| ACLR                | Adjacent channel leakage     | f <sub>DAC</sub> = 491.52 MSPS, f <sub>out</sub> = 30.72 MHz,<br>WCDMA TM1                                          |         | 69   |     |         | 77  |     | dDa    |  |

| ACLK                | ratio                        | f <sub>AC</sub> = 491.52 MSPS, f <sub>out</sub> = 153.6 MHz, WCDMA TM1                                              |         | 68   |     |         | 73  |     | dBc    |  |

|                     | Channel isolation            | $f_{DAC} = 500 \text{ MSPS},$<br>$f_{out} = 20 \text{ MHz}$                                                         |         | 90   |     |         | 90  |     | dBc    |  |

## **ELECTRICAL CHARACTERISTICS – DIGITAL SPECIFICATIONS**

Typical values at T  $_{\rm A}$  = 25°C, full temperature range is T  $_{\rm MIN}$  = -40°C to T  $_{\rm MAX}$  = 85°C, DAC sample rate = 500MSPS, 50% clock duty cycle, VDDA33/IOVDD = 3.3V, VDDA18/CLKVDD18/DIGVDD18 = 1.8V, IOUT  $_{\rm FS}$  = 20mA (unless otherwise noted).

|                       | DADAMETERO                                      | TEGT CONDITIONS                  | D              | AC3154  |             | D              | AC316 | 4               |      |

|-----------------------|-------------------------------------------------|----------------------------------|----------------|---------|-------------|----------------|-------|-----------------|------|

|                       | PARAMETERS                                      | TEST CONDITIONS                  | MIN            | TYP I   | MAX         | MIN            | TYP   | MAX             | UNIT |

| CMOS DI               | GITAL INPUTS (RESETB, SDENB, SCLK, S            | SDIO, TXENABLE)                  |                |         |             |                |       |                 |      |

| $V_{IH}$              | High-level input voltage                        |                                  | 0.6x<br>IOVDD  |         |             | 0.6x<br>IOVDD  |       |                 | V    |

| $V_{IL}$              | Low-level input voltage                         | IOVDD = 3.3 V, 2.5 V<br>or 1.8 V |                |         | .25×<br>VDD |                |       | 0.25×<br>IOVDD  | V    |

| I <sub>IH</sub>       | High-level input current                        |                                  | -40            |         | 40          | -40            |       | 40              | μΑ   |

| I <sub>IL</sub>       | Low-level input current                         |                                  | -40            |         | 40          | -40            |       | 40              | μΑ   |

| DIGITAL               | OUTPUTS - CMOS INTERFACE (SDOUT,                | SDIO)                            |                |         |             |                |       |                 |      |

| V <sub>OH</sub>       | High-level output voltage                       | IOVDD = 3.3 V, 2.5 V, or 1.8 V   | 0.85×<br>IOVDD |         |             | 0.85×<br>IOVDD |       |                 | V    |

| $V_{OL}$              | Low-level output voltage                        |                                  |                |         | 125×<br>VDD |                |       | 0.125×<br>IOVDD | ٧    |

| SERIAL F              | PORT TIMING                                     |                                  |                |         |             |                |       |                 |      |

| t <sub>s(SENDB)</sub> | Setup time, SDENB to rising edge of SCLK        |                                  | 20             |         |             | 20             |       |                 | ns   |

| t <sub>s(SDIO)</sub>  | Setup time, SDIO to rising edge of SCLK         |                                  | 10             |         |             | 10             |       |                 | ns   |

| t <sub>h(SDIO)</sub>  | Hold time, SDIO from rising edge of SCLK        |                                  | 5              |         |             | 5              |       |                 | ns   |

| t <sub>(SCLK)</sub>   | Period of SCLK                                  |                                  | 100            |         |             | 100            |       |                 | ns   |

| t <sub>(SCLKH)</sub>  | High time of SCLK                               |                                  | 40             |         |             | 40             |       |                 | ns   |

| t <sub>(SCLKL)</sub>  | Low time of SCLK                                |                                  | 40             |         |             | 40             |       |                 | ns   |

| t <sub>d(DATA)</sub>  | Data output delay after falling edge of SCLK    |                                  |                | 10      |             |                | 10    |                 | ns   |

| T <sub>RESET</sub>    | Minimum RESTB pulsewidth                        |                                  |                |         |             |                |       |                 |      |

| LVDS IN               | TERFACE (D[x0]P/N, DA[x0]P/N , DB[x0            | ]P/N , DA_CLKP/N, DB_            | _CLKP/N,       | DATACLK | P/N, :      | SYNCP/N,       | ALIGN | IP/N)           |      |

| $V_{A,B+}$            | Logic high differential input voltage threshold |                                  | 175            |         |             | 175            |       |                 | mV   |

| $V_{A,B-}$            | Logic low differential input voltage threshold  |                                  |                |         | -175        |                |       | -175            | mV   |

| V <sub>COM</sub>      | Input Common Mode Range                         |                                  | 1.0            | 1.2     | 2.0         | 1.0            | 1.2   | 2.0             | V    |

| Z <sub>T</sub>        | Internal termination                            |                                  | 85             | 110     | 135         | 85             | 110   | 135             | Ω    |

| C <sub>L</sub>        | LVDS input capacitance                          |                                  |                | 2       | -           |                | 2     |                 | pF   |

Submit Documentation Feedback

## **ELECTRICAL CHARACTERISTICS – DIGITAL SPECIFICATIONS (continued)**

NSTRUMENTS

Typical values at T  $_{\rm A}$  = 25°C, full temperature range is T  $_{\rm MIN}$  = -40°C to T  $_{\rm MAX}$  = 85°C, DAC sample rate = 500MSPS, 50% clock duty cycle, VDDA33/IOVDD = 3.3V, VDDA18/CLKVDD18/DIGVDD18 = 1.8V, IOUT  $_{\rm FS}$  = 20mA (unless otherwise noted).

|         |               |                                               |         |           | D   | AC3154 |     | DAC3164 |      |     |      |

|---------|---------------|-----------------------------------------------|---------|-----------|-----|--------|-----|---------|------|-----|------|

|         |               | PARAMETERS                                    | TEST CO | NDITIONS  | MIN | TYP    | MAX | MIN     | TYP  | MAX | UNIT |

| LVDS IN | PUT TIM       | ING: SINGLE BUS SINGLE CLOCK                  | MODE    | "         |     |        | ,   |         |      |     |      |

|         |               |                                               | config3 |           |     |        |     |         |      |     |      |

|         |               |                                               | datadly | clkdly    |     |        |     |         |      |     |      |

|         |               |                                               | 0       | 0         |     | -20    |     |         | -20  |     |      |

|         |               |                                               | 0       | 1         |     | -120   |     |         | -120 |     |      |

|         |               |                                               | 0       | 2         |     | -220   |     |         | -220 |     |      |

|         |               |                                               | 0       | 3         |     | -310   |     |         | -310 |     |      |

|         |               |                                               | 0       | 4         |     | -390   |     |         | -390 |     |      |

|         |               | D[x0] valid to DATACLK rising or falling edge | 0       | 5         |     | -480   |     |         | -480 |     |      |

| s(DATA) | Setup<br>time |                                               | 0       | 6         |     | -560   |     |         | -560 |     | ps   |

|         |               | Taming dags                                   | 0       | 7         |     | -630   |     |         | -630 |     |      |

|         |               |                                               | 1       | 0         |     | 70     |     |         | 70   |     |      |

|         |               |                                               | 2       | 0         |     | 150    |     |         | 150  |     |      |

|         |               |                                               | 3       | 0         |     | 230    |     |         | 230  |     |      |

|         |               |                                               | 4       | 0         |     | 330    |     |         | 330  |     |      |

|         |               |                                               | 5       | 0         |     | 430    |     |         | 430  |     |      |

|         |               |                                               | 6       | 0         |     | 530    |     |         | 530  |     |      |

|         |               |                                               | 7       | 0         |     | 620    |     |         | 620  |     |      |

|         |               |                                               | congfig | 3 Setting |     |        |     |         |      |     |      |

|         |               |                                               | datadly | clkdly    |     |        |     |         |      |     |      |

|         |               |                                               | 0       | 0         |     | 310    |     |         | 310  |     |      |

|         |               |                                               | 0       | 1         |     | 390    |     |         | 390  |     |      |

|         |               |                                               | 0       | 2         |     | 480    |     |         | 480  |     |      |

|         |               |                                               | 0       | 3         |     | 560    |     |         | 560  |     |      |

|         |               |                                               | 0       | 4         |     | 650    |     |         | 650  |     |      |

|         |               |                                               | 0       | 5         |     | 740    |     |         | 740  |     |      |

| h(DATA) | Hold<br>time  | D[x0] valid to DATACLK rising or falling edge | 0       | 6         |     | 850    |     |         | 850  |     | ps   |

|         | 0             | 9 0090                                        | 0       | 7         |     | 930    |     |         | 930  |     |      |

|         |               |                                               | 1       | 0         |     | 200    |     |         | 200  |     |      |

|         |               |                                               | 2       | 0         |     | 100    |     |         | 100  |     |      |

|         |               |                                               | 3       | 0         |     | 20     |     |         | 20   |     |      |

|         |               |                                               | 4       | 0         |     | -60    |     |         | -60  |     |      |

|         |               |                                               | 5       | 0         |     | -140   |     |         | -140 |     |      |

|         |               |                                               | 6       | 0         |     | -220   |     |         | -220 |     |      |

|         |               |                                               | 7       | 0         | ·   | -290   |     |         | -290 |     |      |

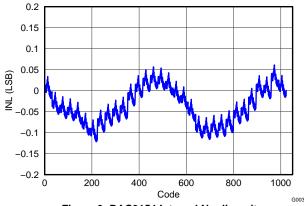

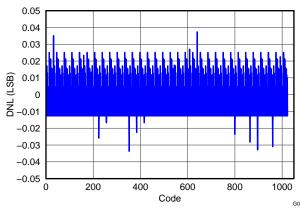

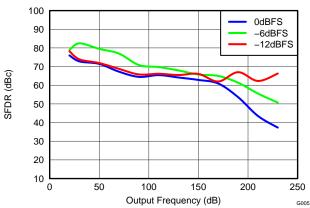

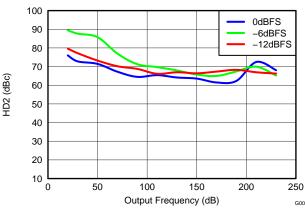

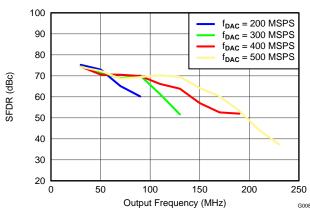

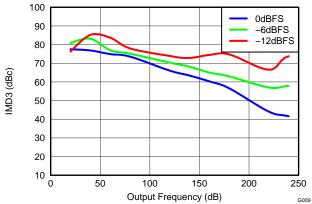

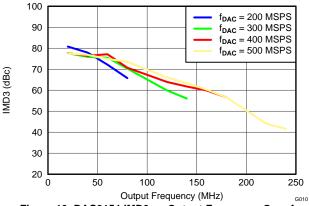

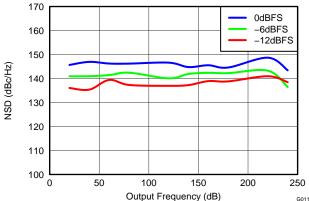

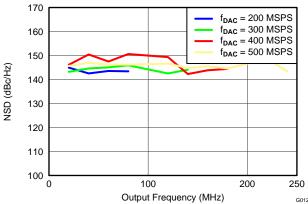

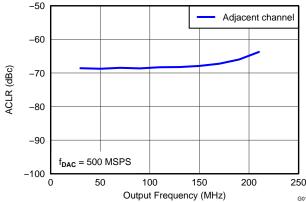

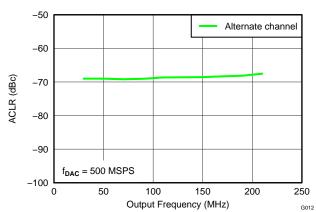

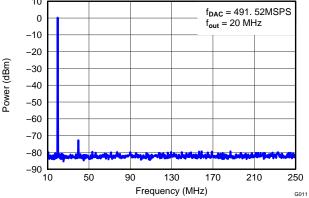

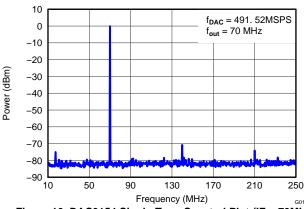

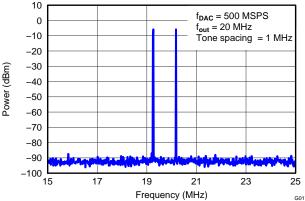

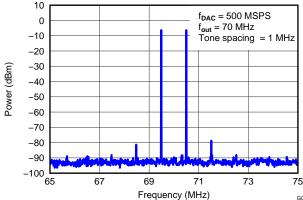

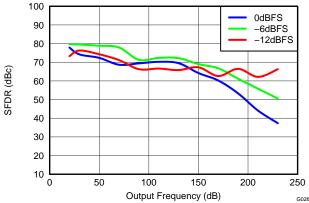

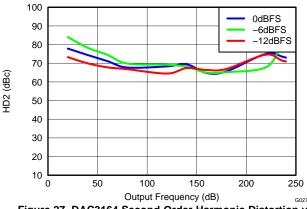

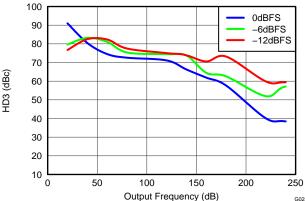

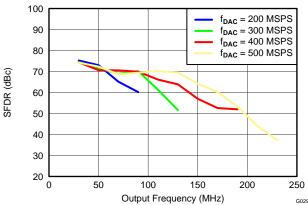

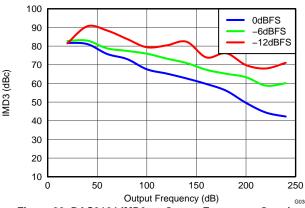

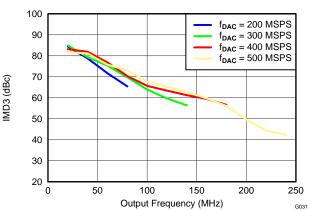

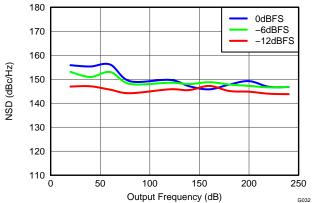

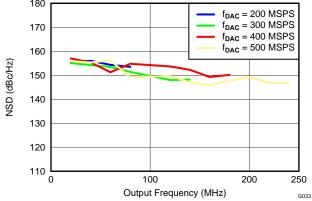

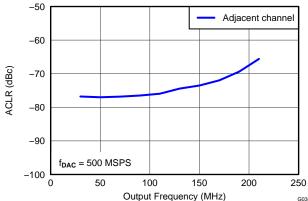

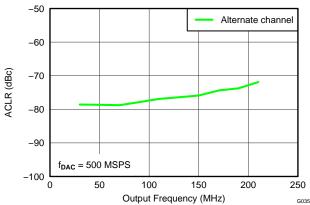

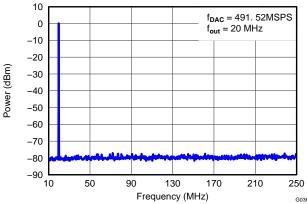

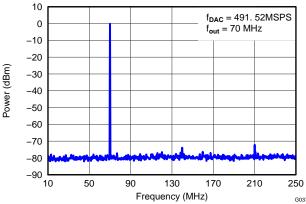

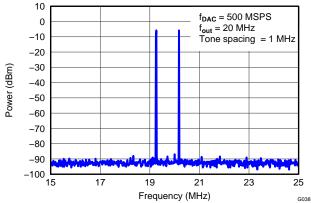

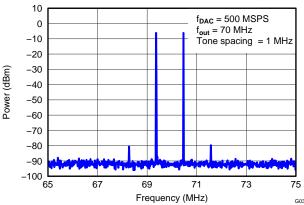

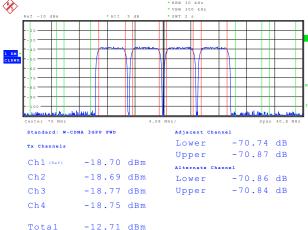

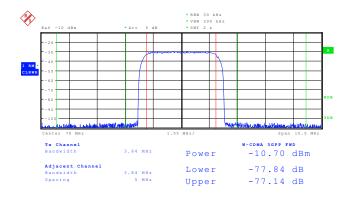

#### TYPICAL CHARACTERISTICS

All plots are at 25°C, nominal supply voltages,  $f_{DAC} = 500MSPS$ , 50% clock duty cycle, 0-dBFS input signal and 20mA full-scale output current (unless otherwise noted).

Figure 3. DAC3154 Integral Nonlinearity

**ISTRUMENTS**

Figure 4. DAC3154 Differential Nonlinearity

Figure 5. DAC3154 SFDR vs Output Frequency Over Input Scale

Figure 6. DAC3154 Second-Order Harmonic Distortion vs Output Frequency Over Input Scale

Figure 7. DAC3154 Third-Order Harmonic Distortion vs Output Frequency Over Input Scale

Figure 8. DAC3154 SFDR vs Output Frequency Over fDAC

## TYPICAL CHARACTERISTICS (continued)

All plots are at 25°C, nominal supply voltages,  $f_{DAC} = 500MSPS$ , 50% clock duty cycle, 0-dBFS input signal and 20mA full-scale output current (unless otherwise noted).

Figure 9. DAC3154 IMD3 vs Output Frequency Over Input Scale

Figure 10. DAC3154 IMD3 vs Output Frequency Over fDAC

Figure 11. DAC3154 NSD vs Output Frequency Over Input Scale

Figure 12. DAC3154 NSD vs Output Frequency Over fDAC

Figure 13. DAC3154 ACLR (Adjacent Channel) vs Output Frequency

Figure 14. DAC3154 ACLR (Alternate Channel) vs Output Frequency

## TYPICAL CHARACTERISTICS (continued)

All plots are at 25°C, nominal supply voltages,  $f_{DAC} = 500MSPS$ , 50% clock duty cycle, 0-dBFS input signal and 20mA fullscale output current (unless otherwise noted).

Figure 15. DAC3154 Single-Tone Spectral Plot (IF = 20MHz)

**NSTRUMENTS**

Figure 16. DAC3154 Single-Tone Spectral Plot (IF = 70MHz)

Figure 17. DAC3154 Two-Tone Spectral Plot (IF = 20MHz)

Figure 18. DAC3154 Two-Tone Spectral Plot (IF = 70MHz)

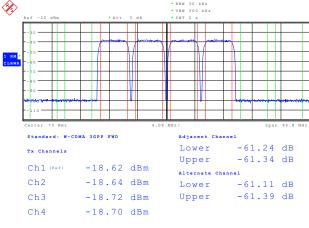

**WCDMA Test Mode 1**

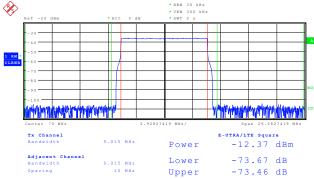

Figure 20. DAC3154 ACPR Single-Carrier WCDMA Test Mode 1

Total

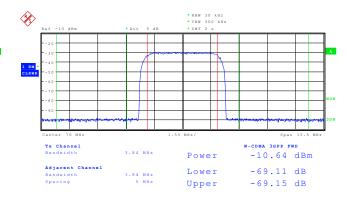

### TYPICAL CHARACTERISTICS (continued)

All plots are at 25°C, nominal supply voltages, f<sub>DAC</sub> = 500MSPS, 50% clock duty cycle, 0-dBFS input signal and 20mA fullscale output current (unless otherwise noted).

**NSTRUMENTS**

Figure 21. DAC3154 ACPR LTE 10-MHz FDD E-TM 1.1

Figure 22. DAC3154 ACPR LTE 20-MHz FDD E-TM 1.1

Figure 25. DAC3164 Differential Nonlinearity

### **TYPICAL CHARACTERISTICS (continued)**

All plots are at 25°C, nominal supply voltages,  $f_{DAC} = 500MSPS$ , 50% clock duty cycle, 0-dBFS input signal and 20mA full-scale output current (unless otherwise noted).

Figure 26. DAC3164 SFDR vs Output Frequency Over Input Scale

**ISTRUMENTS**

Figure 27. DAC3164 Second-Order Harmonic Distortion vs Output Frequency Over Input Scale

Figure 28. DAC3164 Third-Order Harmonic Distortion vs Output Frequency Over Input Scale

Figure 29. DAC3164 SFDR vs Output Frequency Over fDAC

Figure 30. DAC3164 IMD3 vs Output Frequency Over Input Scale

Figure 31. DAC3164 IMD3 vs Output Frequency Over fDAC

## TYPICAL CHARACTERISTICS (continued)

All plots are at 25°C, nominal supply voltages,  $f_{DAC} = 500MSPS$ , 50% clock duty cycle, 0-dBFS input signal and 20mA full-scale output current (unless otherwise noted).

Figure 32. DAC3164 NSD vs Output Frequency Over Input Scale

Figure 33. DAC3164 NSD vs Output Frequency Over fDAC

Figure 34. DAC3164 ACLR (Adjacent Channel) vs Output Frequency

Figure 35. DAC3164 ACLR (Alternate Channel) vs Output Frequency

Figure 36. DAC3164 Single-Tone Spectral Plot (IF = 20MHz)

Figure 37. DAC3164 Single-Tone Spectral Plot (IF = 70MHz)

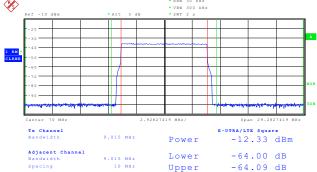

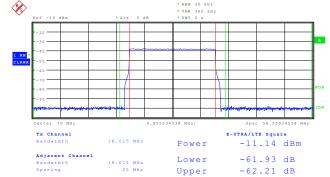

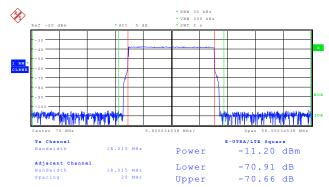

### **TYPICAL CHARACTERISTICS (continued)**

All plots are at 25°C, nominal supply voltages,  $f_{DAC} = 500MSPS$ , 50% clock duty cycle, 0-dBFS input signal and 20mA full-scale output current (unless otherwise noted).

Figure 38. DAC3164 Two-Tone Spectral Plot (IF = 20MHz)

INSTRUMENTS

Figure 39. DAC3164 Two-Tone Spectral Plot (IF = 70MHz)

Figure 40. DAC3164 ACPR Four-Carrier WCDMA Test Mode 1

Figure 41. DAC3164 ACPR Single-Carrier WCDMA Test Mode 1

Figure 42. DAC3164 ACPR LTE 10-MHz FDD E-TM 1.1

Figure 43. DAC3164 ACPR LTE 20-MHz FDD E-TM 1.1

Product Folder Links: DAC3154 DAC3164

## **TYPICAL CHARACTERISTICS (continued)**

All plots are at 25°C, nominal supply voltages,  $f_{DAC} = 500MSPS$ , 50% clock duty cycle, 0-dBFS input signal and 20mA fullscale output current (unless otherwise noted).

**STRUMENTS**

### TEXAS INSTRUMENTS

#### **DEFINITION OF SPECIFICATIONS**

Adjacent Carrier Leakage Ratio (ACLR): Defined as the ratio in decible relative to the carrier (dBc) between the measured power within the channel and that of its adjacent channel.

Analog and Digital Power Supply Rejection Ratio (APSSR, DPSSR): Defined as the percentage error in the ratio of the delta IOUT and delta supply voltage normalized with respect to the ideal IOUT current.

Differential Nonlinearity (DNL): Defined as the variation in analog output associated with an ideal 1 LSB change in the digital input code.

**Gain Drift:** Defined as the maximum change in gain, in terms of ppm of full-scale range (FSR) per °C, from the value at ambient (25°C) to values over the full operating temperature range.

**Gain Error:** Defined as the percentage error (in FSR%) for the ratio between the measured full-scale output current and the ideal full-scale output current.

**Integral Nonlinearity (INL):** Defined as the maximum deviation of the actual analog output from the ideal output, determined by a straight line drawn from zero scale to full scale.

**Intermodulation Distortion (IMD3):** The two-tone IMD3 is defined as the ratio (in dBc) of the 3rd-order intermodulation distortion product to either fundamental output tone.

**Offset Drift:** Defined as the maximum change in DC offset, in terms of ppm of full-scale range (FSR) per °C, from the value at ambient (25°C) to values over the full operating temperature range.

Offset Error: Defined as the percentage error (in FSR%) for the ratio between the measured mid-scale output current and the ideal mid-scale output current.

**Output Compliance Range:** Defined as the minimum and maximum allowable voltage at the output of the current-output DAC. Exceeding this limit may result reduced reliability of the device or adversely affecting distortion performance.

**Reference Voltage Drift:** Defined as the maximum change of the reference voltage in ppm per degree Celsius from value at ambient (25°C) to values over the full operating temperature range.

**Spurious Free Dynamic Range (SFDR):** Defined as the difference (in dBc) between the peak amplitude of the output signal and the peak spurious signal.

**Signal to Noise Ratio (SNR):** Defined as the ratio of the RMS value of the fundamental output signal to the RMS sum of all other spectral components below the Nyquist frequency, including noise, but excluding the first six harmonics and dc.

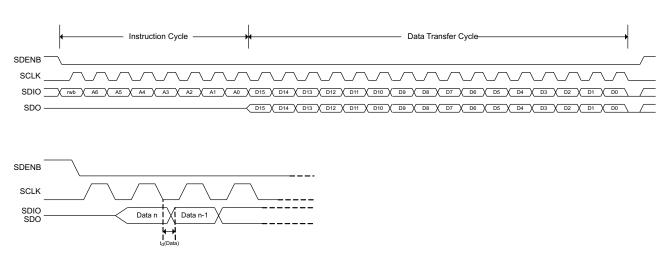

### **TIMING DIAGRAMS**

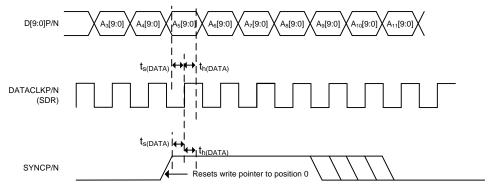

Figure 45. DAC3154 Input Timing Diagram for Dual Channel DDR Mode

22

www.ti.com SLAS960 -MAY 2013

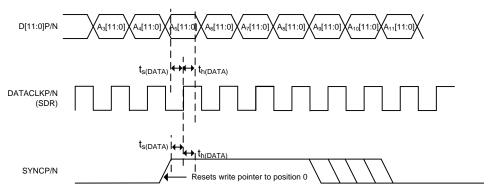

Figure 46. DAC3154 Input Timing Diagram for Single Channel SDR Mode

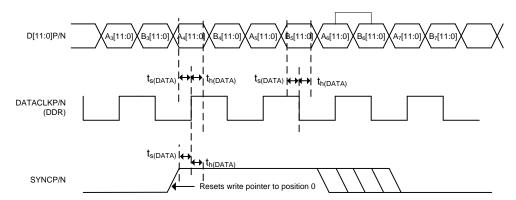

Figure 47. DAC3164 Input Timing Diagram for Dual Channel DDR Mode

Figure 48. DAC3164 Input Timing Diagram for Single Channel SDR Mode

**NSTRUMENTS**

# TEXAS INSTRUMENTS

### **DATA INPUT FORMATS**

Table 1. DAC3154 Dual Channel DDR Mode

|                         | В                   | ITS                  |

|-------------------------|---------------------|----------------------|

| DIFFERENTIAL PAIR (P/N) | DATACLK RISING EDGE | DATACLK FALLING EDGE |

| D9                      | A9                  | В9                   |

| D8                      | A8                  | B8                   |

| D7                      | A7                  | В7                   |

| D6                      | A6                  | B6                   |

| D5                      | A5                  | B5                   |

| D4                      | A4                  | B4                   |

| D3                      | А3                  | В3                   |

| D2                      | A2                  | B2                   |

| D1                      | A1                  | B1                   |

| D0                      | A0                  | В0                   |

| SYNC                    | FIFO Write Reset    | _                    |

Table 2. DAC3154 Single Channel SDR Mode

|                         | В                   | ITS                  |

|-------------------------|---------------------|----------------------|

| DIFFERENTIAL PAIR (P/N) | DATACLK RISING EDGE | DATACLK FALLING EDGE |

| D9                      | А9                  |                      |

| D8                      | A8                  |                      |

| D7                      | A7                  |                      |

| D6                      | A6                  |                      |

| D5                      | A5                  |                      |

| D4                      | A4                  |                      |

| D3                      | А3                  |                      |

| D2                      | A2                  |                      |

| D1                      | A1                  |                      |

| D0                      | A0                  |                      |

| SYNC                    | FIFO Write Reset    | _                    |

Table 3. DAC3164 Dual Channel DDR Mode

|                         | В                   | ITS                  |  |  |

|-------------------------|---------------------|----------------------|--|--|

| DIFFERENTIAL PAIR (P/N) | DATACLK RISING EDGE | DATACLK FALLING EDGE |  |  |

| D11                     | A11                 | B11                  |  |  |

| D10                     | A10                 | B10                  |  |  |

| D9                      | A9                  | В9                   |  |  |

| D8                      | A8                  | B8                   |  |  |

| D7                      | A7                  | В7                   |  |  |

| D6                      | A6                  | B6                   |  |  |

| D5                      | A5                  | B5                   |  |  |

| D4                      | A4                  | B4                   |  |  |

| D3                      | А3                  | В3                   |  |  |

| D2                      | A2                  | B2                   |  |  |

| D1                      | A1                  | B1                   |  |  |

| D0                      | A0                  | В0                   |  |  |

| SYNC                    | FIFO Write Reset    | -                    |  |  |

Submit Documentation Feedback

www.ti.com

## Table 4. DAC3164 Single Channel DDR Mode

|                         | В                   | ITS                  |

|-------------------------|---------------------|----------------------|

| DIFFERENTIAL PAIR (P/N) | DATACLK RISING EDGE | DATACLK FALLING EDGE |

| D11                     | A11                 |                      |

| D10                     | A10                 |                      |

| D9                      | А9                  |                      |

| D8                      | A8                  |                      |

| D7                      | A7                  |                      |

| D6                      | A6                  |                      |

| D5                      | A5                  |                      |

| D4                      | A4                  |                      |

| D3                      | А3                  |                      |

| D2                      | A2                  |                      |

| D1                      | A1                  |                      |

| D0                      | A0                  |                      |

| SYNC                    | FIFO Write Reset    | _                    |

## TEXAS INSTRUMENTS

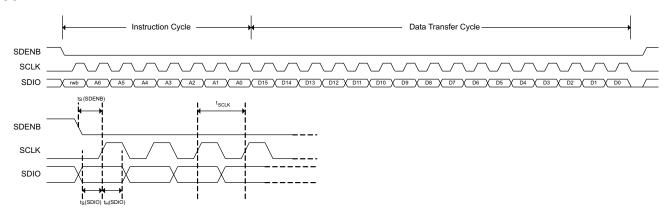

#### SERIAL INTERFACE DESCRIPTION

The serial port of the DAC3154/DAC3164 is a flexible serial interface which communicates with industry standard microprocessors and microcontrollers. The interface provides read/write access to all registers used to define the operating modes of DAC3154/DAC3164. It is compatible with most synchronous transfer formats and can be configured as a 3 or 4 pin interface by *sif4\_ena* in register config0, bit9. In both configurations, SCLK is the serial interface input clock and SDENB is serial interface enable. For 3 pin configuration, SDIO is a bidirectional pin for both data in and data out. For 4 pin configuration, SDIO is data in only and SDO is data out only. Data is input into the device with the rising edge of SCLK. Data is output from the device on the falling edge of SCLK.

Each read/write operation is framed by signal SDENB (Serial Data Enable Bar) asserted low. The first frame byte is the instruction cycle which identifies the following data transfer cycle as read or write as well as the 7-bit address to be accessed. Table 5 indicates the function of each bit in the instruction cycle and is followed by a detailed description of each bit. The data transfer cycle consists of two bytes.

Table 5. Instruction byte of the Serial interface